# μPD82C43 CMOS INPUT/OUTPUT EXPANDER FOR μPD8048/C48 FAMILY

## Description

The  $\mu PD82C43$  input/output expander is directly compatible with the  $\mu PD8048/C48$  family of single-chip microcomputers. Using CMOS technology, the  $\mu PD82C43$  provides high drive capabilities while requiring only a single +5 V supply voltage.

The  $\mu$ PD82C43 interfaces to the  $\mu$ PD8048/C48 family through a 4-bit I/O port and offers four 4-bit bidirectional static I/O ports. The ease of expansion allows for multiple  $\mu$ PD82C43s to be added using the bus port.

The bidirectional I/O ports of the  $\mu$ PD82C43 act as an extension of the I/O capabilities of the  $\mu$ PD8048/C48 microcomputer family. They are accessible with their own ANL, MOV, and ORL instructions.

#### **Features**

□ Four 4-bit I/O ports

□ High output drive

□ Logical AND and OR directly to ports

□ Compatible with industry standard 8243

□ Direct extension of resident μPD8048/C48 I/O ports

□ Fully compatible with μPD8048/C48 microcomputer family

□ CMOS technology

□ Single +5 V supply

## **Ordering Information**

| Part<br>Number | Package Type              |

|----------------|---------------------------|

| μPD82C43C      | 24-pin plastic DIP        |

| μPD82C43CX     | 24-pin plastic skinny DIP |

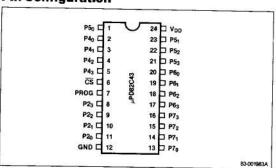

## **Pin Configuration**

### Pin Identification

| No.      | Symbol                           | Function                         |

|----------|----------------------------------|----------------------------------|

| 1, 23-21 | P5 <sub>0</sub> -P5 <sub>3</sub> | 4-bit 1/0 port 5                 |

| 2-5      | P4 <sub>0</sub> -P4 <sub>3</sub> | 4-bit   / 0 port 4               |

| 6        | ĊS                               | Chip select input                |

| 7        | PROG                             | Clock input                      |

| 8-11     | P23-P20                          | 4-bit I / O CPU interface port 2 |

| 12       | GND                              | Ground                           |

| 13-16    | P7 <sub>0</sub> -P7 <sub>3</sub> | 4-bit 1/0 port 7                 |

| 17-20    | P63-P60                          | 4-bit 1/0 port 6                 |

| 24       | V <sub>DD</sub>                  | +5 V power supply                |

## **Pin Functions**

## P20-P23 (Port 2)

A 4-bit bidirectional port which contains the I/O port address and instruction code on a high to low transition of PROG. During a low to high transition of PROG, port 2 contains either the data for a selected output port if a write operation, or the data from a selected output port (before a low to high transition) if a read operation. Data on port 2 may be directly written, read, ANDed or ORed with previous data.

## P40-P43 (Port 4)

A 4-bit I/O port. May be programmed for input (during read), low impedance latched output (after write), or high impedance (after read).

#### P50-P53 (Port 5)

A 4-bit I/O port. May be programmed for input (during read), low impedance latched output (after write), or high impedance (after read).

## P60-P63 (Port 6)

A 4-bit I/O port. May be programmed for input (during read), low impedance latched output (after write), or high impedance (after read).

## P70-P73 (Port 7)

A 4-bit I/O port. May be programmed for input (during read), low impedance latched output (after write), or high impedance (after read).

## CS (Chip Select)

A chip select input. A high on  $\overline{\text{CS}}$  inhibits any change of output or internal status.

## PROG (Clock Input)

A high to low transition on PROG indicates that the opcode and the addressed port information are available on port 2. A low to high transition indicates that data is available on port 2.

### Ground

Ground.

## V<sub>DD</sub> (Power Supply)

+5 V power supply input.

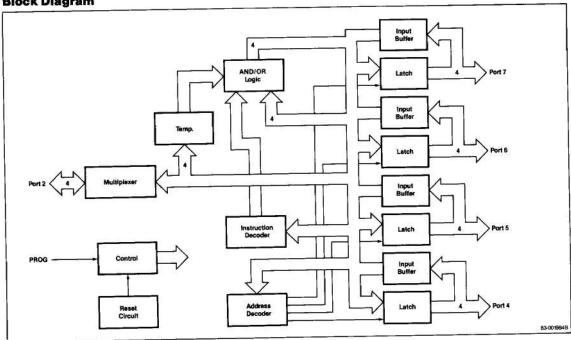

**Block Diagram**

## **Absolute Maximum Ratings**

T<sub>A</sub> = 25°C

| Power supply voltage, V <sub>DD</sub>   | 0.5744 7774                                                       |

|-----------------------------------------|-------------------------------------------------------------------|

|                                         | -0.5 V to +7 V(1)                                                 |

| Input voltage, V <sub>I</sub>           | $-0.3 \mathrm{V}$ to $\mathrm{V}_{\mathrm{DD}}$ +0.3 $\mathrm{V}$ |

| Output voltage, V <sub>O</sub>          | -0.3 V to V <sub>DD</sub> +0.3 V                                  |

| Operating temperature, T <sub>OPT</sub> | -40°C to +85°C                                                    |

| Storage temperature, T <sub>STG</sub>   | -65°C to +150°C                                                   |

| Power dissipation, PD                   | 1.0W                                                              |

#### Note:

Note:

(1) With respect to ground.

Comment: Exposing the device to stresses above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational sections of the specification. Exposure to absolute maximum rating conditions for extended periods may affect device raliability. device reliability.

# **DC Characteristics**

$T_A = -40$  °C to +85 °C;  $V_{DD} = +5$  V ±10%

| Parameter                                     |                      | Limits              |     |          |      | Test                                     |

|-----------------------------------------------|----------------------|---------------------|-----|----------|------|------------------------------------------|

|                                               | Symbol               | Min                 | Тур | Max      | Unit | Conditions                               |

| Input voltage<br>high                         | V <sub>tH</sub>      | V <sub>DD</sub> -2  | .0  | $V_{DD}$ | ٧    |                                          |

| Input voltage<br>low                          | V <sub>IL</sub>      | -0.3                |     | +0.8     | ٧    |                                          |

| Output voltage<br>high (port 4-7)             | V <sub>OH1</sub>     | V <sub>DD</sub> -0  | .5  |          | ٧    | $I_{OH} = -240 \mu A$                    |

| Output voltage<br>high (port 2)               | V <sub>OH2</sub>     | V <sub>D0</sub> -0. | .5  |          | ٧    | $I_{OH} = -100 \mu\text{A}$              |

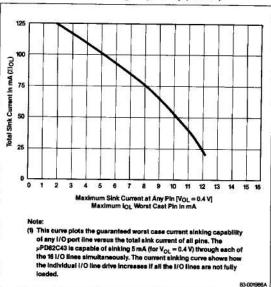

| Output voltage<br>low (port 4-7)              | V <sub>0&amp;1</sub> |                     |     | +0.45    | ٧    | I <sub>OL</sub> = 5 mA, (Note<br>1)      |

| Output voltage<br>low (port 7)                | V <sub>OL2</sub>     |                     |     | +1       | ٧    | $I_{OL} = +20 \text{mA}$                 |

| Output voltage<br>low (port 2)                | V <sub>OL3</sub>     | Was -               |     | +0.45    | ٧    | $I_{0L} = 0.6  \text{mA}$                |

| Sum of all I <sub>OL</sub><br>from 16 outputs | IOL                  |                     |     | 80       | mA   | 5 mA each pin                            |

| Input leakage<br>current (port<br>4-7)        | l <sub>IL1</sub>     |                     |     | ±1       | μА   | V <sub>IN</sub> = V <sub>DD</sub> to 0 V |

| nput leakage<br>current (port 2,<br>CS, PROG) | I <sub>IL2</sub>     |                     |     | ±1       | μА   | $V_{IN} = V_{DD}$ to 0 V                 |

| DD supply current                             | I <sub>DD1</sub>     |                     | 100 | 300      | μΑ   |                                          |

| Power down<br>supply current                  | I <sub>DD2</sub>     | 9100.12             | 1   | 10       | μА   |                                          |

|                                               | 2.50                 |                     |     |          |      |                                          |

(1) Refer to graph of additional sink current drive.

# DC Characteristics (cont)

$T_A = -40$  °C to +85 °C;  $V_{DD} = +2.5$  V to +6 V

| Parameter                                     |                  | Limits               |      |                 |      | 1-2007                      |

|-----------------------------------------------|------------------|----------------------|------|-----------------|------|-----------------------------|

|                                               | Symbol           | Min                  | Тур  | Max             | Unit | Test<br>Conditions          |

| Input voltage<br>high                         | V <sub>IH</sub>  | 0.7 V <sub>DD</sub>  |      | V <sub>DD</sub> | ٧    |                             |

| Input voltage<br>low                          | V <sub>IL</sub>  | -0.3                 |      | +0.18 V         | DD V |                             |

| Output voltage<br>high (port 4-7)             | V <sub>OH1</sub> | 0.75 V <sub>DD</sub> |      |                 | ٧    | $I_{OH} = -120 \mu A$       |

| Output voltage<br>high (port 2)               | V <sub>0H2</sub> | 0.75 V <sub>DD</sub> |      | - 10            | ٧    | $I_{OH} = -50 \mu\text{A}$  |

| Output voltage<br>low (port 4-7)              | V <sub>OL1</sub> |                      |      | +0.45           | ٧    | $I_{OL} = +2.5 \text{mA}$   |

| Output voltage<br>low (port 7)                | V <sub>OL2</sub> |                      |      | +1              | ٧    | $I_{OL} = +7 \text{mA}$     |

| Output voltage<br>low (port 2)                | V <sub>OL3</sub> |                      |      | +0.45           | ٧    | $I_{0L} = +0.3  \text{mA}$  |

| Output current<br>low (port 4-7)              | lor              |                      |      | 40              | mA   | +2.5 mA each pin            |

| Input leakage<br>current (port<br>4-7)        | IL1              |                      | W.C. | ±1              | μА   | $V_{IN} = V_{DD}$ to 0 V    |

| nput leakage<br>current (port 2,<br>CS, PROG) | I <sub>IL2</sub> |                      |      | ±1              | μА   | $V_{IN} = V_{DD}$ to 0 V    |

| DD supply                                     | I <sub>DD1</sub> |                      | 100  | 300             | μΑ   | Operation mode,<br>(Note 1) |

| ower down<br>upply current                    | I <sub>DD2</sub> | 15                   | 1    | 10              | μΑ   | Standby mode                |

## Note:

(1)  $I_{OH} = 0 \mu A$ , PROG pulse cycle =  $5 \mu s$  min.

AC Characteristics  $T_A = -40\,^{\circ}\text{C to } +85\,^{\circ}\text{C}, V_{DD} = +5\,\text{V} \pm 10\,\%$

| 4.817                                     |                 | Limits |     |     |      | Test        |

|-------------------------------------------|-----------------|--------|-----|-----|------|-------------|

| Parameter                                 | Symbol          | Min    | Тур | Max | Unit | Conditions  |

| Code valid<br>before PROG                 | tA              | 100    |     |     | ns   | 80 pF load  |

| Code valid after<br>PROG                  | t <sub>B</sub>  | 0      |     |     | ns   | 20 pF load  |

| Data valid before<br>PROG                 | t <sub>C</sub>  | 200    |     | 100 | ns   | 80 pF load  |

| Data valid after<br>PROG                  | to              | 20     |     | -35 | ns   | 20 pF load  |

| Port 2 floating<br>after PROG             | tн              | 0      |     | 150 | ns   | 20 pF load  |

| PROG negative<br>pulse width              | t <sub>K</sub>  | 700    |     |     | ns   |             |

| Ports 4–7 valid<br>after PROG             | t <sub>PO</sub> | 1000   |     | 700 | ns   | 100 pF load |

| Ports 4-7 valid<br>before / after<br>PROG | t <sub>IP</sub> | 100    |     |     | ns   |             |

| Port 2 valid after<br>PROG                | tacc            | 90     |     | 650 | ns   | 80 pF load  |

| CS valid<br>before / after<br>PROG        | tcs             | 50     |     |     | ns   |             |

## **Timing Waveform**

AC Characteristics T<sub>A</sub> = -40°C to +85°C, V<sub>DD</sub> = +2.5 V to +6 V

| Parameter                                                                     |                 | Limits |        |                                         |      | Test                                              |

|-------------------------------------------------------------------------------|-----------------|--------|--------|-----------------------------------------|------|---------------------------------------------------|

|                                                                               | Symbol          | Min    | Тур    | Max                                     | Unit | Conditions                                        |

| Command input<br>setup time to<br>PROG ↓                                      | t <sub>A</sub>  | 300    |        |                                         | ns   | Port 2 (control,<br>port, address);<br>80 pF load |

| Command input<br>setup time after<br>PROG 4                                   | t <sub>B</sub>  | 0      |        |                                         | ns   | Port 2 (control,<br>port, address);<br>20 pF load |

| Data input setup<br>time to PROG ↑                                            | tc              | 600    |        | - 40                                    | ns   | Port 2 (write<br>mode); 80 pF load                |

| Data input hold<br>time after<br>PROG †                                       | t <sub>D</sub>  | 80     |        | 117                                     | ns   | Port 2 (write<br>mode); 20 pF load                |

| Data float delay<br>time from<br>PROG †                                       | t <sub>H</sub>  | 0      |        | 400                                     | ns   | Port 2 (read mode)<br>20 pF load                  |

| PROG pulse<br>width                                                           | t <sub>K</sub>  | 2      |        | ======================================= | μS   |                                                   |

| CS input setup<br>time to PROG ‡<br>CS input hold<br>time after<br>PROG †     | tcs             | 200    | 70 8   |                                         | ns   |                                                   |

| Data output<br>delay time from<br>PROG †                                      | t <sub>PO</sub> |        | 0.5-15 | 2                                       | ns   | Port 4–7; 100 pF<br>load                          |

| Data input setup<br>time to PROG ↓<br>Data input hold<br>time after<br>PROG ↑ | t <sub>IP</sub> | 100    |        |                                         | ns   | Port 4-7                                          |

| Data output<br>delay time from<br>PROG ↓                                      | tacc            |        |        | 3.5                                     | μS   | Port 2; 80 pF load                                |

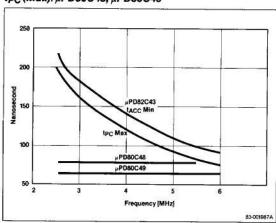

Figure 2. t<sub>ACC</sub> (Min)/µPD82C43 vs t<sub>PC</sub> (Max)/µPD80C48, µPD80C49

### **Functional Description**

The I/O capabilities of the  $\mu$ PD8048/C48 family can be enhanced in four I/O port increments of 4 bits each using one or more  $\mu$ PD82C43s. These additional I/O lines are addressed as ports 4–7. The following lists the operations which can be performed on ports 4–7.

- Logical AND accumulator to port

- Logical OR accumulator to port

- Transfer port to accumulator

- · Transfer accumulator to port

Port 2 (P20-P23) forms the 4-bit bus through which the  $\mu$ PD82C43 communicates with the host processor. The PROG output from the  $\mu$ PD8048/C48 family provides the necessary timing to the  $\mu$ PD82C43. There are two 4-bit nibbles involved in each data transfer. The first nibble contains the opcode and port address followed by the second nibble containing the 4-bit data. Multiple  $\mu$ PD82C43s can be used for additional I/O. The output lines from the  $\mu$ PD8048/C48 family can be used to form the chip selects for additional  $\mu$ PD82C43s.

#### Power On Initialization

Applying power to the  $\mu$ PD82C43 sets ports 4-7 to the high impedance mode and port 2 to the input mode. The state of the PROG pin at power on may be either high or low. The PROG pin must make a high to low transition in order to exit from the power on mode. The power on sequence is initiated any time V<sub>DD</sub> drops below 1V. Table 1 following shows how the first 4-bit nibble of a data transfer instruction is decoded.

Table 1. Port 2 Instruction Decoding

| P23 | P2 <sub>2</sub> | Instruction Code | P2 <sub>1</sub> | P2 <sub>0</sub> | Address Code |  |

|-----|-----------------|------------------|-----------------|-----------------|--------------|--|

| 0   | 0               | Read             | 0               | 0               | Port 4       |  |

| 0   | 1               | Write            | 0               | 1               | Port 5       |  |

| 1   | 0               | ORLD             | 1               | 0               | Port 6       |  |

| 1   | 1               | ANLD             | 1               | 1               | Port 7       |  |

For example, a 0010 appearing on P23-P20, respectively, would result in a read of port 6.

#### **Read Mode**

There is one read mode in the  $\mu$ PD82C43. A falling edge on the PROG pin latches the op code and port address from input port 2. The port address and read operation are then decoded, causing the appropriate outputs to be high impedance and the input buffers switched on. The rising edge of PROG terminates the read operation. The port (4, 5, 6, or 7) that was selected by the port address (P21-P20) is returned to the high impedance mode, and port 2 is switched to the input mode.

## μPD82C43

Generally, in the read mode a port will be an input and in the write mode it will be an output. If during program operation the  $\mu$ PD82C43's modes are changed, the first read pulse immediately following a write should be ignored. The subsequent read signals are valid. Reading a port will then force that port to a high impedance state.

## **Write Modes**

There are three write modes in the  $\mu$ PD82C43. The MOVD P<sub>p</sub>, A instruction from the  $\mu$ PD8048/C48 family writes the new data directly to the specified port (4, 5, 6,

or 7). The old data previously latched at that port is lost. The ORLD  $P_p,\; A$  instruction performs a logical OR between the new data and the data currently latched at the selected port. The result is then latched at that port. The final write mode uses the ANLD  $P_p,\; A$  instruction. It performs a logical AND between the new data and the data currently latched at the specified port. The result is latched at that port.

The data remains latched at the selected port following the logical manipulation until new data is written to that port.